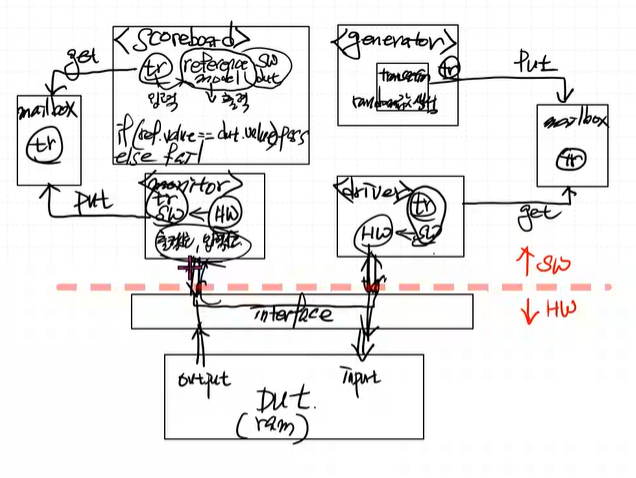

오늘은 기존에 공부하던 UVM을 위한 System Verilog의 연장선을 배웠습니다.아래의 그림에서, 오른쪽 부분 Generator, Mailbox, Driver, Interface, DUT에 대해서만 배웠었다면이번에는 왼쪽 부분인 ScoreBoard, Mailbox, Monitor, Interface, DUT에 대해 배우고 전체 Testbench에 대해서 배웠습니다. 왼쪽부분에 간략히 설명하자면, 오른쪽 부분과 데칼코마니 처럼 비슷합니다. DUT에서 나오는 Output을 Interface의 전선다발로 받게 되고, Monitor가 H/W로 받은 전선 다발을 풀어 S/W의 Tr로 변경해 줍니다.변경된 Tr은 Mailbox에 들어가고, 이를 감지하는 ScoreBoard가 tr을 받아와 reference m..