오늘의 메인 키워드는 FSM(Finite State Machine)이라고 할 수 있겠습니다.

일단, 먼저 Verilog 문법들에 대해서 배웠습니다.

우리가 코드를 작성하는 데 사용하는 자료형.

net 자료형 : 회로 소자/블록의 하드웨어적인 연결에 사용

ㄴ ex) wire, tri

ㄴ tri = Multiple driving sources가 혀용됨

variable 자료형 : always, initial 블록 내부의 절차형 할당문에 의해 값을 받는 변수

ㄴ ex) reg, integer, time *reg : 절차형 할당문에 의해 값을 받는 변수의 자료형

주로, 하드웨어 연결을 위한 wire, 값을 받기 위한 reg를 가장 많이 씁니다.

논리값은 4개의 논리값을 가지고 있습니다. (x와 Z가 눈에 띕니다)

- 1 = True

- 0 = False

- x = don't care --> 0,1,Z 가능

- Z = high Impedence --> 구동신호가 없는 상태

여러 특징들도 있습니다.

벡터 : 2비트 이상의 벡터를 위한 독립된 자료형이 없으며, reg, wire 선언에 함께 선언

[msb : lsb]을 갖는 다중 비트의 net 또는 reg 자료형

ㄴ ex) reg [7:0] a == 8bit a

배열 : 특정 자료형의 원소들을 다차원 변수로 묶기 위해 사용됨

ㄴ ex) reg[7:0] mem_A [0:255] == 8비트 레지스터 256개로 구성되는 메모리 선언

메모리 : reg형 요소를 갖는 배열, 메모리 전체가 단일 할당문으로 값을 할당 받을 수 없음

ㄴ ex) reg [1:n] Reg_A

Parameter : 상수값 설정을 위해 사용 ( 가독성, 유연성)

ㄴ local parameter vs parameter : 외부에서 변경X , 외부에서 변경 가능

ㄴ ex) parameter Byte = 8

parameter [31:0] dec_const = 1'b1;

다양한 연산자들(논리, 비트, 조건, 시프트,등가)이 있지만, C언어와 동일합니다. 그 중, 조금(?) 신기했던

결합 연산자 : ({ }) 를 사용하면 비트가 다른 두 값을 결합할 수 있습니다.

ㄴ ex) 4bit sum과 1bit carry를 결합해 4bit a+b를 뽑아냄

wire [3:0] a, b, sum

wire carry

assign ({carry, sum} = a + b

문법은 뒤로하고, FSM을 만들기 위한 중요한 개념이 시작됩니다.

조합 (Cominational Logic) 회로 : clk로 설계되지 않는 회로

ㄴ ex) gate , decoder/encoder , mux, 비교기, Adder

논리 (Sequential Logic) 회로 : clk로 설계되는 회로

ㄴ ex) counter , clk divider, F/F, Shift Register

여기에서 중요한 latch와 Flip Flop의 개념이 나오게됩니다.

논리회로는 clk을 사용하고, 출력이 현재의 값과 과거의값들에 의존한다고 알고 있습니다. 그 말은 기억할 수 있고, 메모리의 기능을 할 수 있다는 것입니다.

기본적인 Latch인 SR LATCH의 경우, 귀환(Feedback) 적 특성을 가지고 있고, 입력이 변하면 출력이 바로 변환합니다.

NOR 2개를 이어 붙인 회로를 보면, 입력이 1이 들어가게되면 다른 NOR 회로에 반전되어 0으로 들어가고, 다시 반전되어 1을 출력하게 됩니다. 다시 이 1이 첫번째 NOR에 들어가고 반전되어 0을 출력하고 0이 들어가서 1이 되고 등등.. 의 순환을 합니다.

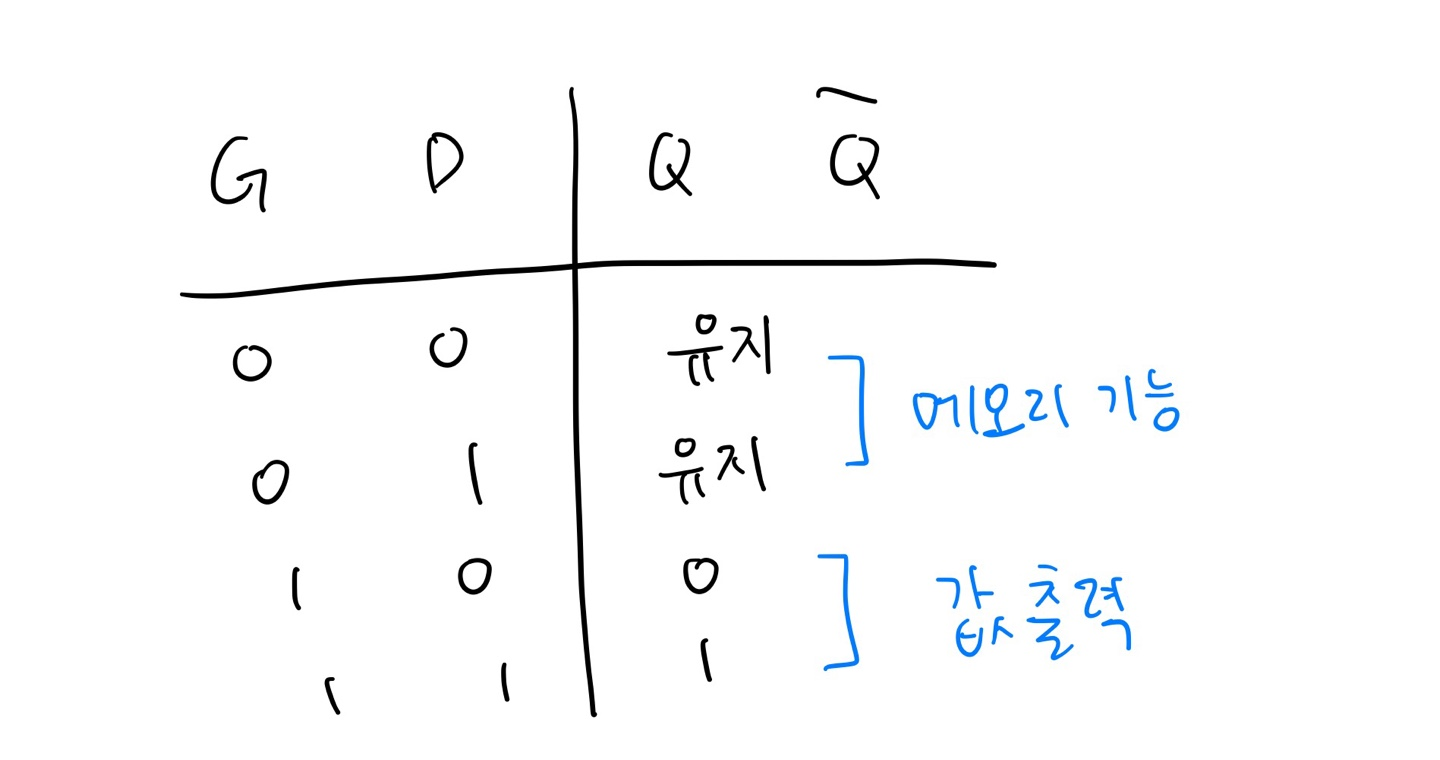

그리하여 진리표를 구성하면 아래와 같습니다. S와 R이 모두 0 일때, Q와 `Q의 값이 똑같이 유지되는 것이 메모리의 기능을 하게 됩니다.

하지만, 문제는, S=1 R=1일 경우 입니다. 일단, Q와 `Q는 서로 반전 되어있는 상태여야 하는데, 서로 같은 값을 지니고 있습니다. 별거 아닌 것 같지만, 이게 왜 문제가 되냐면 Q와 `Q이 0,0 인상태로 다시 Feedback 되면, 다음 출력은 1,1 이되고 다시 Feedback 되면 0,0이 되면서 0,0 , 1,1의 무한 출력 루프가 생성되게 됩니다.

그리하여, 이러한 문제를 해결하기 위해 D Latch라는 개념이 등장합니다. D Latch는 기존 SR Latch에 Gate와 단일 입력 D를 추가합니다. 회로도와 진리표는 아래와 같습니다.

진리표를 살펴보면, Gate가 0 일 경우, 우리가 원하던 기능인 메모리 기능을 하게 되고, 문제가 되던 1,1 입력의 경우에도 출력이 잘 되는 것을 확인할 수 있습니다. 이러한 메모리 기능은 Gate에 Pulse를 집어 넣음으로 확인할 수 있습니다.

그림과 같이 Pulse를 넣게 되면, NOR gate 기반의 D Latch이므로, 진리표에 따라, 출력 Q는 다음과 같이 나오게 됩니다.

Pulse의 값이 1인 경우 즉, 위의 진리표에서 G의값이 1인 경우, 인가되는 D의 값을 그대로 출력하는 것을 확인할 수 있습니다. 그리하여 Pulse가 HIGH 상태인 구간에서는 Q가 D의 값을 똑같이 출력합니다.

하지만, Pulse의 값이 0인 경우에는 즉, 진리표에서 G의 값이 0인 경우, 모든 값들은 전 값과 동일하게 유지가 됩니다. 그리하여, LOW 구간 동안에는 이전 HIGH 구간에서 출력된 값을 그대로 유지하게 됩니다.

이러한 동작으로 Latch는 clk은 없지만, 메모리의 기능을 하는 비동기적인 순차 논리 회로라고 할 수 있습니다.

이렇게 SR Latch, D Latch에 대해 알아 보았습니다. 이제 Flip Flop에 대해서도 배워 보겠습니다.

이제껏 알아본 Latch에서 clk의 기능이 없다는 것이 아쉽습니다. 그래서, clk의 기능을 탑재하여 2개의 D Latch를 이어 붙혀 생성하게 됩니다.

왜 clk를 사용하냐면, Flip Flop의 경우 펄스가 0->1 또는 1->0에서 변하는 edge에 의해 동작하기 때문에 clk를 사용한다.

무슨 말이냐면, 위의 회로도와 pulse의 값을 대조하며 값을 출력해 보겠습니다.

먼저 첫번째 D Latch의 경우, NOT Gate가 붙어 있습니다. Low Level Trigger 입니다. 그리하여 펄스가 low일 경우에 값을 출력하고 High일 경우에는 값을 유지하여 MQ를 출력합니다.

출력된 MQ는 두번째 D Latch에 입력되고 D Latch는 High Level Trigger 처럼 동작하여 펄스가 High일 때 값을 출력, low일 때 값을 유지하며 SQ를 만들어 냅니다.

출력되는 SQ의 결과를 통해, Flip Flop은 Pulse의 edge가 유지되는 동안 값을 이전 값을 유지하는 것 을 볼 수 있습니다. 즉 , 메모리의 기능을 하는 것을 확인할 수 있습니다.

이렇게 저장 기능인 메모리에 대해 FSM 실습을 진행하였습니다.

FSM(Finite State Machine) : 규칙에 따라 상태를 천이하며 동작하는 시스템

그 중, moore 모델을 만들었습니다. moore 모델은 출력이 현재 상태를 기반으로 결정이 되는 모델입니다

상태를 나타내는 2bit State, 3bit의 스위치를 통해 값을 입력하고 2bit의 led를 통해 출력하는 모델입니다.

입력되는 3bit의 스위치의 값에 따라 상태가 천이하게 되며, 각 상태마다 led를 출력하는 방식이 다릅니다. 그리하여 상태를 천이하면서 led를 제어하는 그러한 시스템입니다.

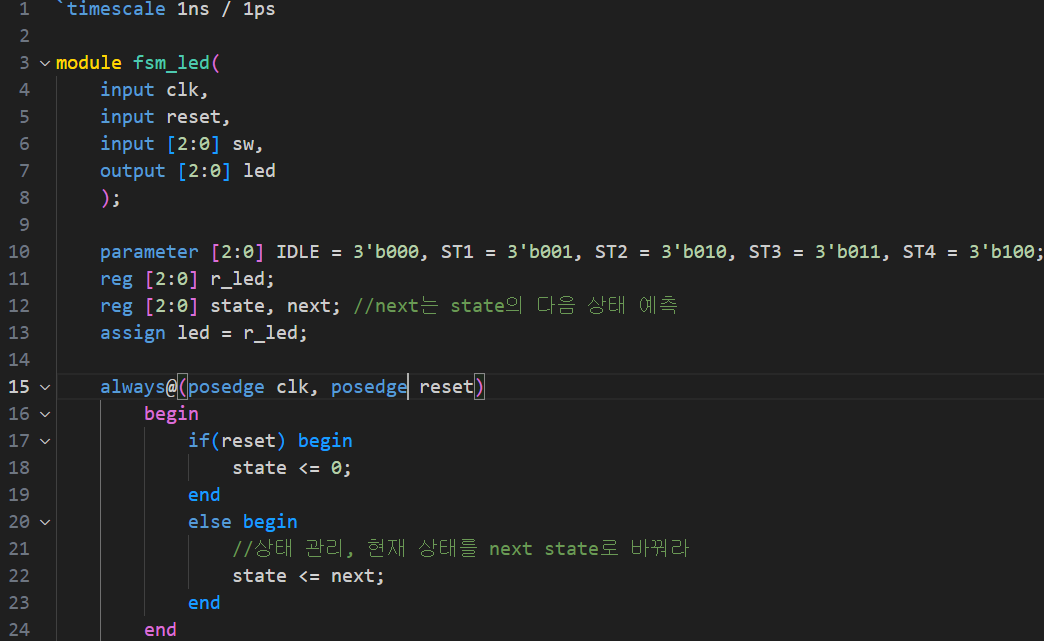

코드 자체는 많이 어렵지 않았다. 클럭과 리셋의 상승 에지를 항상 보고 있으며, reset이 되는 경우 상태를 초기화 시킨다. 만약 set 되지 않았다면, state는 천이할 준비를 하면 된다. 현재의 state와 스위치 입력(sw)의 조합으로 다음 상태(next)를 결정하여 순회하는 모델이다. 그리고 각 상태마다 각기 다른 LED를 출력하도록 설정하였다.

그에 대한 추가 실습으로 아래와 같은 State Machine도 만들었다.

이번엔 영상도 찍었습니다. 손에 가려서 잘은 보이지 않지만, led를 눈크게 뜨고 보면 동작도 그림과 같이 동작함을 확인할 수 있습니다. (보시고 싶으신 분은 참조하시면 되겠습니다...ㅎ)

이렇게 오늘은 메모리에 대한 이론과, 이를 활용한 FSM에 대해서 배우게 되었습니다. 대학 시절 FPGA 수업을 들으며 열심히 FSM에 대해 배웠던 기억 덕분인지 이해하는데에는 어려움이 많이 없었던 것 같습니다. 하지만, 잊고 있었던 Latch, Flip Flop 그리고 클럭의 타이밍에 대한 기본적인 개념들은 오랜만에 보니 기억이 날듯 말듯... ㅋ.. 다음엔 들으면 바로 설명할 수 있을 정도로 머리속에 넣어야겠습니다.

그림 1) SR Latch 회로도 https://blog.naver.com/leeyunghuk1/220980312714

그림 3) D Latch 회로도 https://electbros.com/latch/

'[HARMAN] 세미콘 아카데미 > 공부내용' 카테고리의 다른 글

| [Harman 세미콘 아카데미] Day_23(Verilog) (0) | 2025.03.07 |

|---|---|

| [Harman 세미콘 아카데미] Day_22(Verilog) (0) | 2025.03.06 |

| [Harman 세미콘 아카데미] Day_20(Verilog) (0) | 2025.03.04 |

| [Harman 세미콘 아카데미] Day_19(Verilog) (0) | 2025.03.02 |

| [Harman 세미콘 아카데미] Day_18(Verilog) (0) | 2025.03.02 |