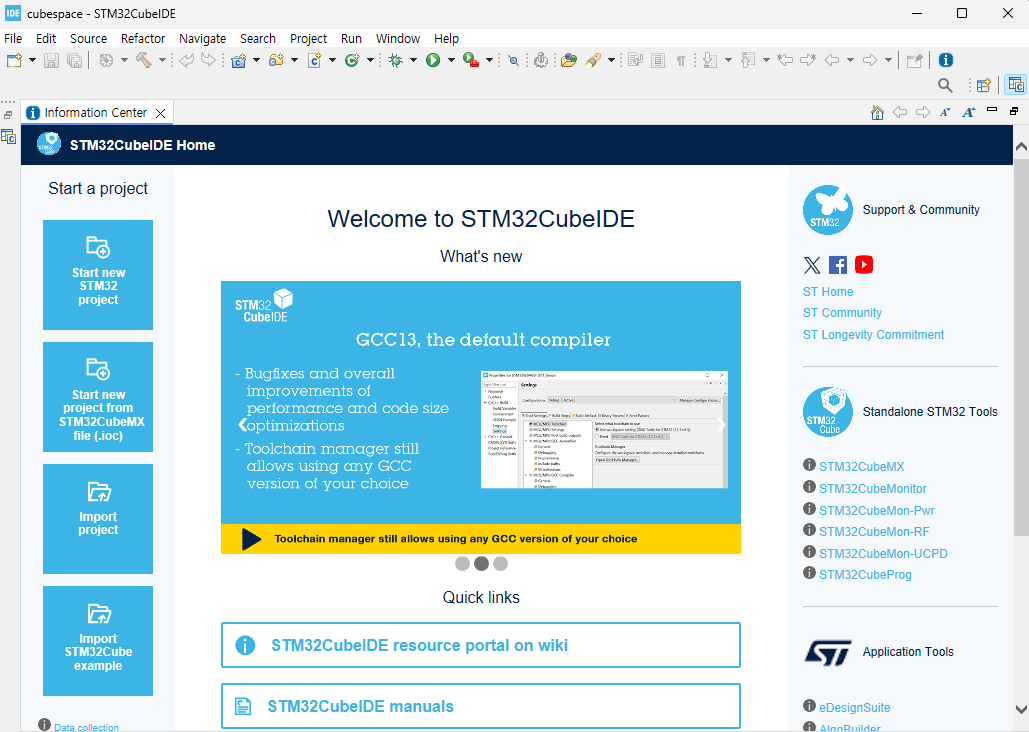

오늘은 STM32Nucleo 보드를 통해 카메라 모듈을 제어하는 것을 배웁니다. 카메라 모듈은 OV7670 모델을 사용합니다.ST32Nucleo 보드와 Basys3보드와의 I2C 통신을 시켜서 카메라를 사용하게 됩니다. Basys3 - STM32Nucleo - Camera 와 같이 연결됩니다. STM32 Cube IDE를 활용하여 코딩을 진행합니다. STM32F411RE Board를 선택하고 파일을 생성하면 아래와 같은 칩이 생성됩니다. 카메라 모듈에 대한 Block Diagram을 그려보면 Camera와 VGA RGB Port 사이에 1Frame을 담는 Buffer가 존재하게 됩니다. RAM과 같은 동작을 하면서, Camera의 Data를 RAM에 Write하고 VGA RGB Port에 Read하여..